抢先一步掀起红色风暴 英伟达被弯道超车

搭积木一样造芯片。

据不完全统计,目前半导体行业已开发出约 1000 种封装类型,按互连类型来划分,其中包括了引线键合、倒装芯片、晶圆级封装 (WLP) 和硅通孔 (TSV)等,无数个die通过互联器件相连接,构成了如今日渐繁盛的封装市场。

其中的先进封装,成为了近两年最受关注和欢迎的领域,先进制程进展越缓慢,它的重要性就愈发突出, AMD、英特尔和英伟达这传统的“御三家”纷纷涉足,从2D封装转战2.5D封装,还向3D封装这座高峰发起了挑战。

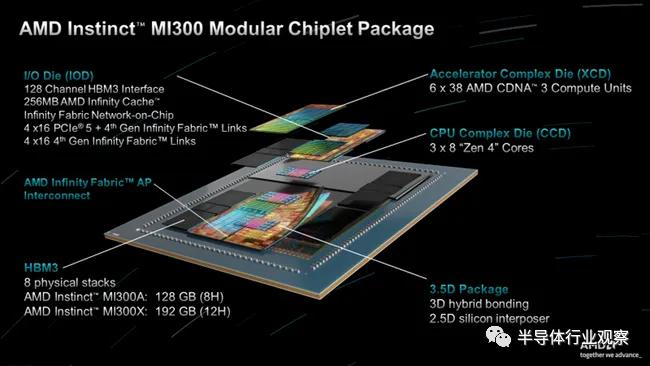

2023年6月,AMD在旧金山正式推出了MI300X与MI300A两款AI加速器, 其中MI300X 采用了8 XCD,4个IO die,8个HBM3堆栈,高达256MB的AMD Infinity Cache和3.5D封装的设计,支持 FP8 和稀疏性等新数学格式,是一款全部面向 AI 和 HPC 工作负载的设计,而它的晶体管也达到了1530 亿颗,成为了 AMD 迄今为止制造的最大芯片。

AMD表示,MI300X 在人工智能推理工作负载中的性能比英伟达 H100高出1.6倍,在训练工作中的性能与 H100相当,从而为业界提供了亟需的高性能替代品,以取代英伟达的GPU。此外,这些加速器的 HBM3 内存容量也是英伟达 GPU 的两倍多,达到惊人的 192 GB,使其 MI300X 平台能够支持每个系统两倍多的 LLM,并能运行比 H100 HGX 更大的模型。

最受瞩目的当然还是AMD所宣称的3.5D封装,AMD表示,通过引入3D混合键合和2.5D的硅中介层,实现了全新的“3.5D封装”技术。

AMD 高级副总裁兼企业研究员 Sam Naffziger 表示:“这是真正令人惊叹的硅堆栈,提供了业界目前已知的最高密度性能。这一集成采用了台积电的两种技术,即 SoIC(集成芯片系统)和 CoWoS(芯片基板芯片)。前者(SoIC)使用混合键合技术将较小的芯片堆叠在较大的芯片之上,无需焊料就能直接连接每个芯片上的铜垫,其帮助高速缓冲存储V-Cache 芯片堆叠在最高端的 CPU 芯片上,而后者(CoWos)将芯片堆叠在一块更大的硅片上,这块硅片被称为内插板(interposer),用于容纳高密度互连。”

当英伟达还在H200中使用台积电CoWoS的2.5D封装时,AMD却率先一步,实现了台积电SoIC 3D封装和CoWoS 2.5D封装的结合,而它更早之前对Chiplet的布局,似乎早已为这次弯道超车做足了准备。

搭积木一样造芯片

首先我们来回顾一下MI300X和MI300A的具体架构,根据AMD官方的解释,MI300系列采用了台积电的 3D 混合键合 SoIC(集成电路上硅)技术,在四个底层 I/O 芯片之上对各种计算元件进行 3D 堆叠,无论是 CPU CCD(核心计算芯片)还是 GPU XCD。每个 I/O 芯片可以容纳两个 XCD 或三个 CCD。每个 CCD 与现有 EPYC 芯片中使用的 CCD 相同,每个 CCD 拥有八个超线程 Zen 4 核心。MI300A 使用了其中的三个 CCD 和六个 XCD,而 MI300X 使用了八个 XCD。

所谓 XCD,是AMD在GPU中负责计算的Chiplet,在MI 300X上,8个XCD包含了304 个CDNA 3 计算单元,那就意味着每个计算单元包含了34个CU。作为对比,AMD MI 250X 拥有220个CU,这是一个较大的飞跃。

而HBM 堆栈则采用了 2.5D 封装技术的标准中介层进行连接,每个 I/O 芯片都包含一个 32 通道 HBM3 内存控制器,用于托管 8 个 HBM 堆栈中的两个,从而为该设备提供了总共 128 个 16 位内存通道。MI300X 采用 12Hi HBM3 堆栈,容量为 192GB,而 MI300A 使用 8Hi 堆栈,容量为 128GB。

具体而言,AMD 的 CPU CCD 通过 3D 混合键合到底层 I/O 芯片,通过利用标准 2.5D 封装的GMI3接口进行通信,AMD 为此添加了一个新的焊盘通孔接口,可绕过 GMI3 链路,从而提供垂直堆叠芯片所需的 TSV。

[物价飞涨的时候 这样省钱购物很爽]

还没人说话啊,我想来说几句

据不完全统计,目前半导体行业已开发出约 1000 种封装类型,按互连类型来划分,其中包括了引线键合、倒装芯片、晶圆级封装 (WLP) 和硅通孔 (TSV)等,无数个die通过互联器件相连接,构成了如今日渐繁盛的封装市场。

其中的先进封装,成为了近两年最受关注和欢迎的领域,先进制程进展越缓慢,它的重要性就愈发突出, AMD、英特尔和英伟达这传统的“御三家”纷纷涉足,从2D封装转战2.5D封装,还向3D封装这座高峰发起了挑战。

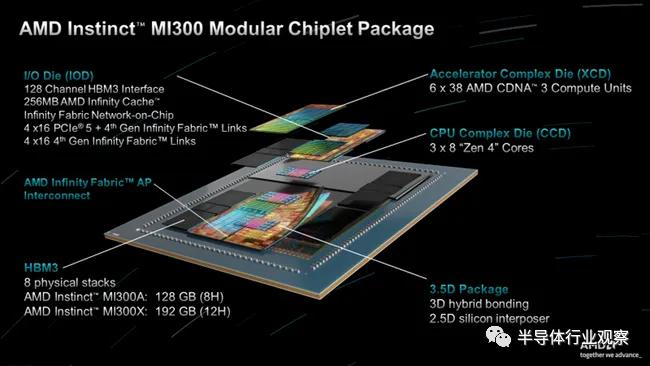

2023年6月,AMD在旧金山正式推出了MI300X与MI300A两款AI加速器, 其中MI300X 采用了8 XCD,4个IO die,8个HBM3堆栈,高达256MB的AMD Infinity Cache和3.5D封装的设计,支持 FP8 和稀疏性等新数学格式,是一款全部面向 AI 和 HPC 工作负载的设计,而它的晶体管也达到了1530 亿颗,成为了 AMD 迄今为止制造的最大芯片。

AMD表示,MI300X 在人工智能推理工作负载中的性能比英伟达 H100高出1.6倍,在训练工作中的性能与 H100相当,从而为业界提供了亟需的高性能替代品,以取代英伟达的GPU。此外,这些加速器的 HBM3 内存容量也是英伟达 GPU 的两倍多,达到惊人的 192 GB,使其 MI300X 平台能够支持每个系统两倍多的 LLM,并能运行比 H100 HGX 更大的模型。

最受瞩目的当然还是AMD所宣称的3.5D封装,AMD表示,通过引入3D混合键合和2.5D的硅中介层,实现了全新的“3.5D封装”技术。

AMD 高级副总裁兼企业研究员 Sam Naffziger 表示:“这是真正令人惊叹的硅堆栈,提供了业界目前已知的最高密度性能。这一集成采用了台积电的两种技术,即 SoIC(集成芯片系统)和 CoWoS(芯片基板芯片)。前者(SoIC)使用混合键合技术将较小的芯片堆叠在较大的芯片之上,无需焊料就能直接连接每个芯片上的铜垫,其帮助高速缓冲存储V-Cache 芯片堆叠在最高端的 CPU 芯片上,而后者(CoWos)将芯片堆叠在一块更大的硅片上,这块硅片被称为内插板(interposer),用于容纳高密度互连。”

当英伟达还在H200中使用台积电CoWoS的2.5D封装时,AMD却率先一步,实现了台积电SoIC 3D封装和CoWoS 2.5D封装的结合,而它更早之前对Chiplet的布局,似乎早已为这次弯道超车做足了准备。

搭积木一样造芯片

首先我们来回顾一下MI300X和MI300A的具体架构,根据AMD官方的解释,MI300系列采用了台积电的 3D 混合键合 SoIC(集成电路上硅)技术,在四个底层 I/O 芯片之上对各种计算元件进行 3D 堆叠,无论是 CPU CCD(核心计算芯片)还是 GPU XCD。每个 I/O 芯片可以容纳两个 XCD 或三个 CCD。每个 CCD 与现有 EPYC 芯片中使用的 CCD 相同,每个 CCD 拥有八个超线程 Zen 4 核心。MI300A 使用了其中的三个 CCD 和六个 XCD,而 MI300X 使用了八个 XCD。

所谓 XCD,是AMD在GPU中负责计算的Chiplet,在MI 300X上,8个XCD包含了304 个CDNA 3 计算单元,那就意味着每个计算单元包含了34个CU。作为对比,AMD MI 250X 拥有220个CU,这是一个较大的飞跃。

而HBM 堆栈则采用了 2.5D 封装技术的标准中介层进行连接,每个 I/O 芯片都包含一个 32 通道 HBM3 内存控制器,用于托管 8 个 HBM 堆栈中的两个,从而为该设备提供了总共 128 个 16 位内存通道。MI300X 采用 12Hi HBM3 堆栈,容量为 192GB,而 MI300A 使用 8Hi 堆栈,容量为 128GB。

具体而言,AMD 的 CPU CCD 通过 3D 混合键合到底层 I/O 芯片,通过利用标准 2.5D 封装的GMI3接口进行通信,AMD 为此添加了一个新的焊盘通孔接口,可绕过 GMI3 链路,从而提供垂直堆叠芯片所需的 TSV。

[物价飞涨的时候 这样省钱购物很爽]

| 分享: |

| Note: | _VIEW_NEWS_FULL |

推荐: